現貨庫存,2小時發貨,提供寄樣和解決方案

熱搜關鍵詞:

隨著電子設備功能不斷增強,時鐘信號的要求也越來越高。時鐘信號作為整個系統的“心臟”,其性能直接影響著系統的整體性能。PLL作為調頻器件,在時鐘信號生成中發揮著重要作用。如何設計一個高性能的PLL成為系統設計人員的重中之重。

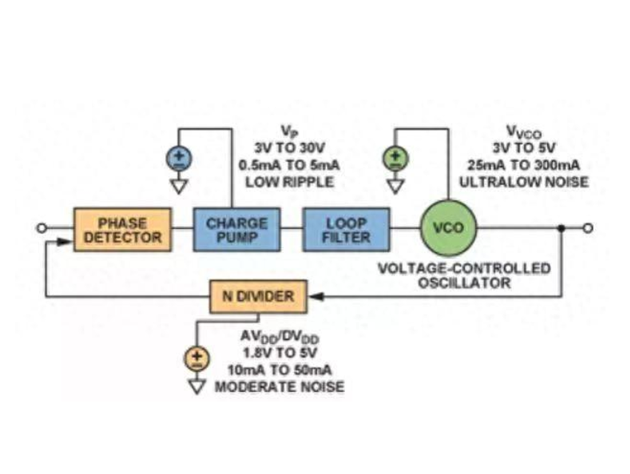

PLL設計的關鍵在于電源管理。穩定的電源供應是PLL正常工作的基礎,電源質量的好壞直接影響著PLL輸出時鐘的穩定性。傳統上,PLL采用單一電源供應,無法滿足不同模塊對電源的需求。此外,單一電源也難以隔離各種電磁干擾,從而影響PLL的時鐘穩定性。

為解決這個問題,我們可以從電源管理模塊入手,為PLL提供多路定制電源。具體來說:

1. 為PLL數字部分和模擬部分單獨提供電源。數字電路對電源質量要求較低,可以直接采用系統電源。而模擬電路對電源噪聲的容忍度小得多,需要單獨設計低噪聲電源為其供電。

2. 為PLL內部關鍵模擬塊單獨設計電源。例如VCO、頻偏電路等對時鐘穩定性影響重大的模擬塊,可以考慮單獨設計電源,進一步降低其電源噪聲影響。

3. 采用多級隔離結構優化電源布局。例如數字電路和模擬電路采用不同電源層隔離;關鍵模擬電路采用單獨電源島隔離。這樣可以有效降低各電源之間的電磁干擾。

4. 采用低噪聲電源技術。例如LT3042這樣的低噪聲線性穩壓器,可以有效濾除電源中的雜散電磁噪聲。

通過上述多路定制電源和優化電源布局,我們實現了對PLL各個部分電源的精細管理。這將有效提高PLL的時鐘穩定性,從而幫助設計出性能更優的PLL。電源管理就是PLL設計的重中之重。如需采購電源管理芯片、申請樣片測試、BOM配單等需求,請加客服微信:13310830171。